Initially, we were thinking of synthesizing our logic into FPGA, but most of the vendors don’t open their bitstream format, and hacking takes a huge amount of time. Now we have changed a new way: we synthesize our logic into PLD (programmable logic device), especially for CPLD or PAL.

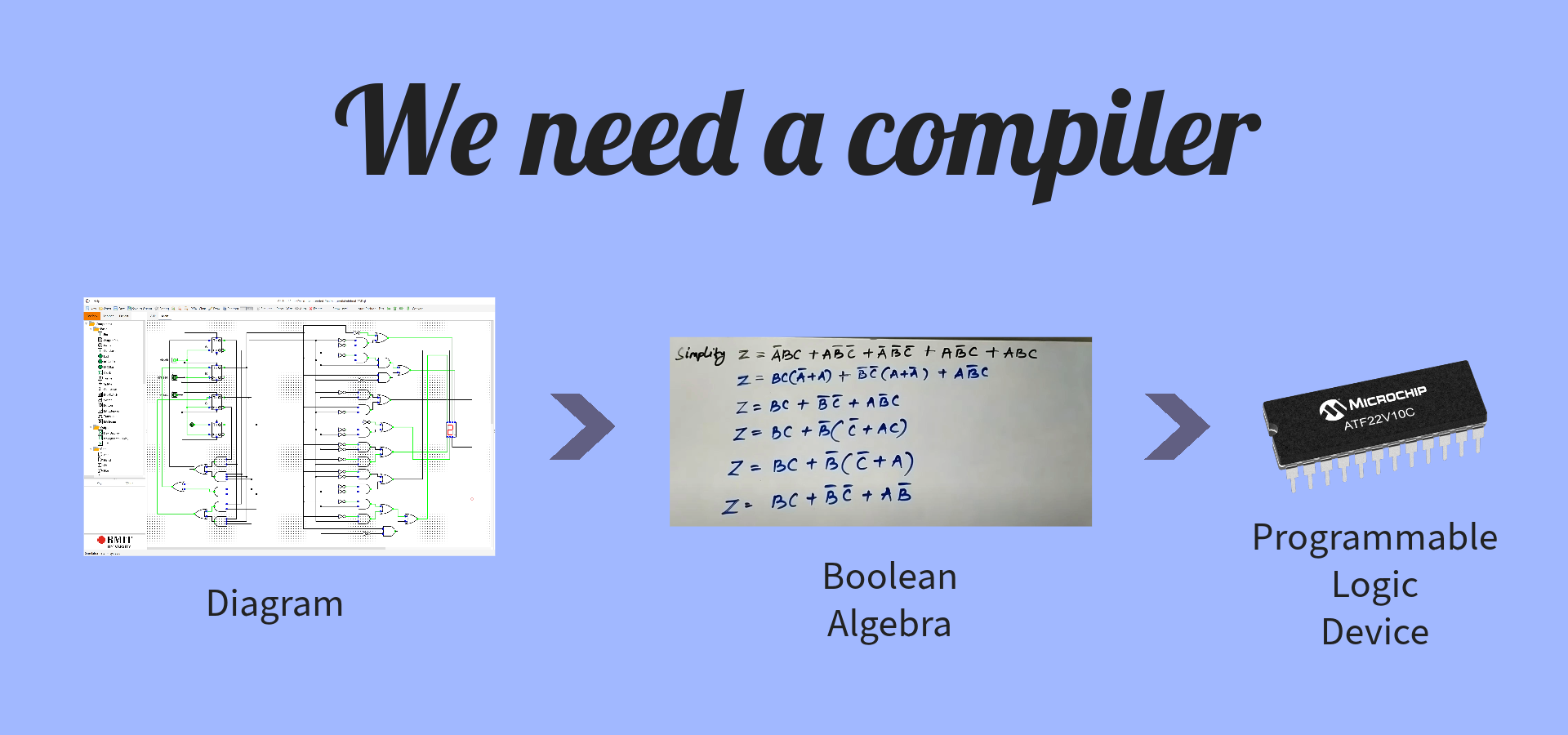

Now we need a logic compiler, converting the diagram data structure which outputs from Quantr-Logic to boolean algebra, and compiles it into PLD format, which can be sent to the programmer to burn the logic.